Is Moore's Law Dead? Unlocking Performance with Photonics

For more than five decades, the advancement of computing technology followed a consistent pattern: greater performance, smaller devices, and lower costs, all on a predictable timeline.

This trajectory, famously captured by Moore’s Law, projected that computing elements on an integrated circuit would increase twofold approximately every couple of years, driving significant improvements in speed, efficiency, and cost per function. This eventually became the implicit benchmark for innovation across industries, from consumer electronics to aerospace, data centres to scientific research.

This pace of progress has shaped not only the performance of our devices but also the economic model underpinning the global tech ecosystem. As chips became more powerful and affordable, the benefits cascaded into everyday applications. Faster processors, energy-efficient sensors, and more capable smartphones were all direct outcomes of this scaling principle.

But today, the industry is approaching fundamental physical boundaries. What was once a reliable roadmap now presents diminishing returns, prompting a shift in strategy. Rather than continuing to scale silicon alone, the focus is moving toward integrating new materials and approaches—ushering in the era of photonics.

The Enduring Principle of Chip Advancement

In 1965, Gordon Moore made a simple observation: the number of transistors on an integrated circuit had been steadily increasing, and if that trend continued, it could double roughly every year.

Over time, as fabrication capabilities matured and real-world data accumulated, the industry adjusted this timeline to roughly every 18 to 24 months. Despite these shifts, the exponential nature of the pattern held steady for decades, serving as a guiding reference for semiconductor development.

Importantly, Moore’s Law is not a scientific law in the formal sense. It does not describe a physical constant, nor is it derived from first principles. Rather, it reflects the industry’s sustained ability to improve chip performance and reduce cost through continuous innovation in design and manufacturing. Its influence extended far beyond the transistor count—it became a strategic benchmark used to set expectations across product planning, investment cycles, and technology roadmaps.

For years, this trajectory enabled a consistent cadence of advancement. Devices grew faster, more compact, and more accessible. At the heart of this progress was the steady evolution of semiconductor process technologies, which made room for denser circuitry and more complex architectures.

This meant that Moore’s Law wasn’t just a prediction; instead, it acted as a powerful motivator that shaped how the industry approached innovation and scale.

Confronting Physical and Economic Barriers

But as transistors edge closer to atomic dimensions, the methods that once sustained decades of progress are now meeting resistance both physically and economically.

The Squeeze on Silicon Scaling

Shrinking transistor dimensions has long been the strategy for improving chip performance, but this approach is now nearing its physical threshold.

At sub-nanometre scales, transistors begin to exhibit quantum mechanical behaviours, such as tunnelling, that interfere with stable operation. The smaller the features become, the harder it is to manage leakage current and thermal dissipation, both of which compromise power efficiency and reliability.

To navigate these constraints, semiconductor manufacturing has become significantly more complex. Producing advanced nodes now requires multiple patterning steps to replicate extremely fine features with precision. These techniques, while necessary, increase fabrication time, introduce more points of failure, and demand tighter integration across design and process teams. As a result, design cycles are longer, and yield management becomes increasingly difficult. The path forward remains open, but no longer linear.

Diminishing Returns on Investment

Pushing into smaller nodes has not only become technically demanding, but also economically unsustainable for many. In fact, according to the Boston Consulting Group (BCG), the cost of developing a modern system-on-chip can now exceed one billion dollars, especially when accounting for specialised processing blocks. As a result, for companies without the scale or resources to absorb such costs, the barriers to entry are growing.

Even when these investments are made, the returns are not what they used to be.

Earlier nodes often brought substantial jumps in performance, efficiency, and transistor density. Today, those benefits are less dramatic. The gains remain, but they come slower, and at greater cost. This deceleration marks a fundamental shift in how the industry measures progress.

This means that Moore’s Law, while still influencing roadmaps in valid ways, no longer delivers exponential results on its own. The focus now shifts to alternative technologies that can pick up where traditional scaling leaves off.

The Quantum Leap: Embracing Photonic Computing

With the limits of transistor scaling coming into sharper focus, the search for fundamentally different computing paradigms is no longer theoretical.

Rather, it has become essential.

Photonic computing offers one such shift, trading electrons for light to unlock performance levels that silicon alone cannot reach.

Pivoting to Photonics

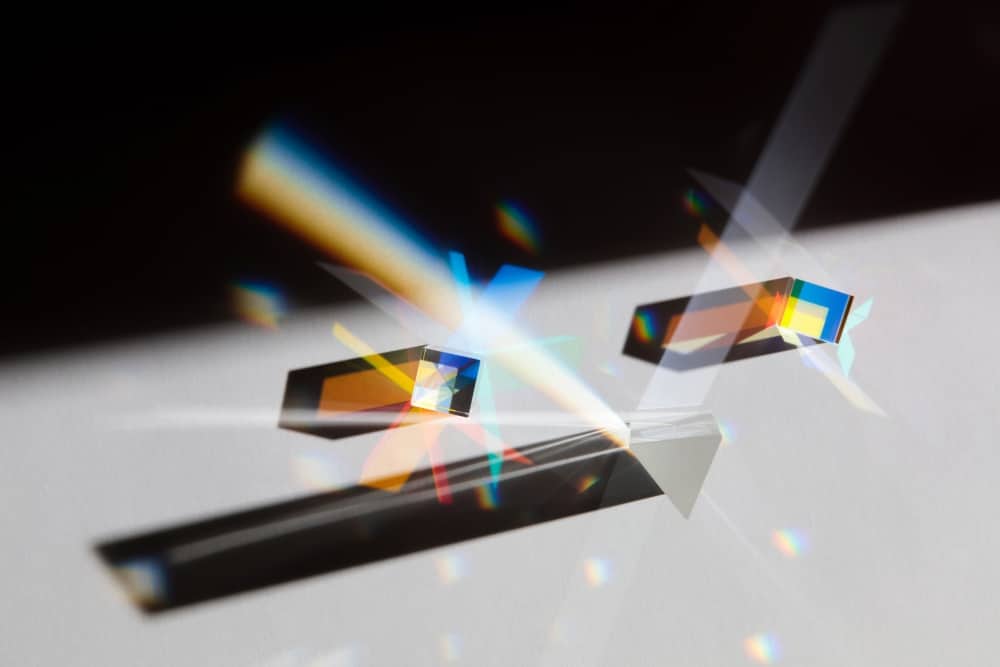

Unlike conventional systems that rely on the movement of electrons, photonic computing uses photons to process and transmit information.

This transition brings significant advantages.

Photons travel at the speed of light, carry more data, and generate less heat compared to their electronic counterparts. These attributes allow for ultra-fast data throughput—a characteristic that aligns closely with the needs of emerging data-intensive workloads.

As computing demands escalate, especially in fields like artificial intelligence, telecommunications, and scientific modelling, photonic chips offer a path forward. Their ability to support high-speed parallelism and energy-efficient processing makes them especially relevant for next-generation applications where latency, power, and bandwidth constraints are critical.

This shift is already underway. The convergence of photonics and AI is laying the foundation for new modes of computation, where light not only moves data but plays an active role in logic and learning.

Advancing Interconnects with Integration

As chip architectures evolve, the bottleneck is no longer confined to logic—it extends to how fast and efficiently data can move between components. This is where photonic interconnects become essential.

Optical waveguides enable high-bandwidth, low-latency data transmission within and between chips, replacing traditional copper traces that increasingly struggle with power loss and signal degradation at scale.

Co-packaged optics (CPO) has emerged as a compelling approach to address this challenge.

By placing optical and electronic components side by side within the same package, CPO shortens channel lengths, lowers energy per bit, and improves signal integrity. This integration reduces the reliance on long copper connections and additional DSP stages that add latency and power draw.

The impact is particularly pronounced in data centre and high-performance computing environments, where demands for bandwidth density and energy efficiency continue to rise. Co-packaged optics not only supports higher throughput but also provides a scalable foundation for future network architectures. As integration techniques mature, CPO will play a central role in extending the performance roadmap beyond what conventional packaging allows, enabling faster, more efficient systems capable of meeting tomorrow’s compute demands.

NSTIC’s Catalytic Role in the Photonics Era

As silicon technology reaches its fundamental constraints, NSTIC plays a critical role in advancing next-generation semiconductor photonics through applied research, infrastructure, and integration expertise.

Advancing Performance Through Heterogeneous Integration

While silicon remains unmatched for CMOS compatibility and cost-effective manufacturing, its optical limitations are well-documented.

For one, it lacks efficient light emission, high-speed modulation via the Pockels effect, and strong light absorption for detection. To overcome these material constraints, NSTIC is focused on photonic heterogeneous integration (PHI), combining best-in-class optical materials onto silicon substrates. This includes bonding thin-film Lithium Niobate for ultra-high-speed modulators, III-V semiconductors for lasers and photodetectors, and Barium Titanate for high-bandwidth, high-efficiency modulation.

By doing so, NSTIC aims to push the boundaries of optical transceivers toward 400G/lane performance—laying the groundwork for data rates exceeding 3.2 Tbps.

Flat Optics: Miniaturising Vision with Advanced Functionality

Flat optics—engineered metasurfaces that manipulate light with nanostructured patterns—are redefining how imaging and sensing systems are built. Unlike traditional optics, these ultra-thin components reduce bulk while adding new optical functionalities.

At NSTIC, flat optics are fabricated using semiconductor-grade wafer-level processes, enabling high-throughput production of thousands of components per 300mm wafer. These devices are being designed not only to replace traditional lenses but to surpass them, addressing challenges in chromatic dispersion, field of view, and spectral performance. With potential applications across consumer electronics, medical imaging, metrology, and biosensing, flat optics is one of the most promising technologies in NSTIC’s research portfolio.

The 300mm Cleanroom Advantage

NSTIC houses a 300mm wafer cleanroom purpose-built for semiconductor photonics innovation. This facility supports full-scale prototyping, testing, and pilot production, enabling seamless transition from R&D to manufacturable solutions.

For companies seeking to accelerate product development in advanced photonics, our cleanroom provides direct access to equipment, process expertise, and proven fabrication flows. It also acts as a key enabler for translating lab-scale concepts, such as flat optics and heterogeneous integration, into scalable technologies ready for market adoption. By bridging the lab-to-fab gap, NSTIC helps reduce development timelines, mitigate technical risk, and prepare IPs for commercial production or foundry transfer.

A New Horizon for Technological Advancement

As NSTIC drives innovation in photonics integration and wafer-level manufacturing, a broader transformation is taking shape—one that redefines how future electronic and optical systems will be designed, built, and deployed across industries. This shift opens up new frontiers in performance, efficiency, and scalability.

Unlocking Exponential Growth

Maintaining progress in semiconductor performance now requires more than just scaling down. The focus is shifting toward hybrid approaches, combining silicon with high-performance photonic materials, rethinking interconnect architectures, and embedding new functionalities at the chip level. This change in direction is not a step back, but a step beyond, enabling devices to deliver more performance, greater bandwidth, and enhanced adaptability. By moving beyond the limitations of single-material systems, this new model of progress creates room for exponential growth through convergence, not just miniaturisation.

Transformative Opportunities Across Sectors

From datacentres to diagnostics, photonics is unlocking cross-sector breakthroughs that redefine what’s possible across performance, scale, and impact.

- Data Infrastructure: Photonic interconnects and co-packaged optics enable data centres to operate at higher speeds and greater energy efficiency. These technologies support growing demands from cloud computing, AI training workloads, and real-time analytics.

- Advanced Sensing: Flat optics technologies are accelerating breakthroughs in compact imaging systems for LiDAR, microscopy, and precision metrology, which is essential for automotive, consumer, and industrial applications.

- Next-Gen Compute: Photonic computing offers a path forward for AI and high-performance computing by addressing bottlenecks in bandwidth, latency, and energy consumption that traditional architectures struggle to overcome.

- Healthcare & Biotech: Photonics-powered systems are transforming bio-imaging and molecular diagnostics by enabling high-resolution, portable solutions that enhance sensitivity and enable earlier detection.

NSTIC stands ready to collaborate with partners driving change across these sectors. With deep expertise in silicon photonics and access to our 300mm wafer cleanroom, heterogeneous integration platforms, and expert teams in flat optics and advanced photonics, companies can accelerate the translation of innovation into scalable, next-generation solutions.